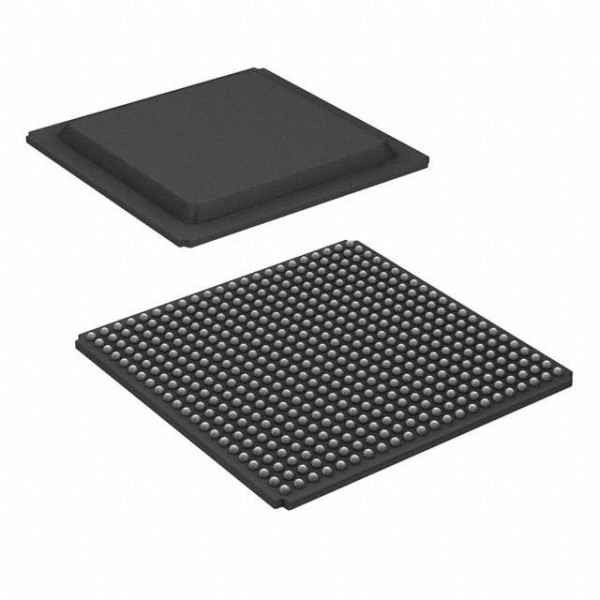

XC6SLX75-2FGG484C Field Programmable Gate Array

♠ wehewehe huahana

| Huahana Huahana | Waiwai Hiʻona |

| Mea hana: | Xilinx |

| Māhele Huahana: | FPGA - ʻĀpana Programmable Gate Array |

| RoHS: | Nā kikoʻī |

| moʻo: | XC6SLX75 |

| Ka helu o nā Elements Logic: | 74637 LE |

| Ka helu o nā I/Os: | 280 I/O |

| Voltage Hoʻolako - Min: | 1.14 V |

| Voltage Hoʻolako - Max: | 1.26 V |

| Mahana hana liʻiliʻi loa: | 0 C |

| ʻO ka wela hoʻohana kiʻekiʻe loa: | + 85 C |

| Ka helu ʻikepili: | - |

| Ka helu o nā mea lawe uila: | - |

| Kāila kau ʻana: | SMD/SMT |

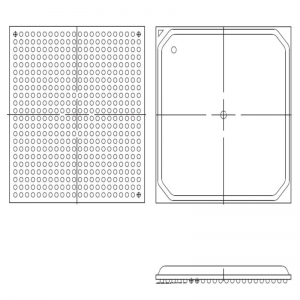

| Pūʻolo / hihia: | FCBGA-484 |

| Brand: | Xilinx |

| Hoʻolaha ʻia ka RAM: | 692 kbit |

| Pākaʻi RAM - EBR: | 3096 kbit |

| ʻO ke alapine hana kiʻekiʻe loa: | 1080 MHz |

| ʻAi ʻoluʻolu: | ʻAe |

| Ka helu o nā poloka Lahui Logic - LABs: | 5831 LAB |

| Voltage lako hana: | 1.2 V |

| ʻAno Huahana: | FPGA - ʻĀpana Programmable Gate Array |

| Ka nui o ka waihona hale hana: | 1 |

| Māhele ʻāpana: | Nā IC Logic Programmable |

| inoa kalepa: | Spartan |

| Huina Wehe: | 1.662748 oz |

♠ Spartan-6 Nānā ʻOhana

Hāʻawi ka ʻohana Spartan®-6 i nā mana hoʻohui ʻōnaehana alakaʻi me ka uku haʻahaʻa haʻahaʻa no nā noi kiʻekiʻe. Hāʻawi ka ʻohana he ʻumikumamākolu i nā densities i hoʻonui ʻia mai ka 3,840 a i ka 147,443 logic cell, me ka hapalua o ka hoʻohana ʻana i ka mana o nā ʻohana Spartan ma mua, a ʻoi aku ka wikiwiki, ʻoi aku ka hoʻopili piha. Kūkulu ʻia ma luna o ka ʻenehana kaʻina hana keleawe haʻahaʻa haʻahaʻa 45 nm e hāʻawi i ke koena maikaʻi loa o ke kumukūʻai, ka mana, a me ka hana, hāʻawi ka ʻohana Spartan-6 i kahi loiloi hou, ʻoi aku ka maikaʻi, ʻelua-kakau 6-input lookup table (LUT) a me kahi koho waiwai o nā poloka pae ʻōnaehana i kūkulu ʻia. Loaʻa kēia mau mea he 18 Kb (2 x 9 Kb) poloka RAM, ʻelua hanauna DSP48A1 slices, SDRAM memory controllers, enhanced mixed-mode clock management blocks, SelectIO™ technology, poweroptimized high-speed serial transceiver blocks, PCI Express® compatible Endpoint blocks, advanced system-level power management modes, auto-detect Device configuration protection and AES enhanced Device configuration protection.

Hāʻawi kēia mau hiʻohiʻona i kahi koho programmable haʻahaʻa haʻahaʻa i nā huahana ASIC maʻamau me ka maʻalahi o ka hoʻohana ʻana. Hāʻawi nā Spartan-6 FPGA i ka hoʻonā maikaʻi loa no nā hoʻolālā loiloi kiʻekiʻe, nā hoʻolālā DSP pili i nā mea kūʻai aku, a me nā noi i hoʻopili ʻia. ʻO Spartan-6 FPGAs ka papahana silikoni papahana no Targeted Design Platforms e hāʻawi ana i nā lako polokalamu i hoʻohui ʻia a me nā ʻāpana lako e hiki ai i nā mea hoʻolālā ke nānā aku i ka hana hou i ka wā e hoʻomaka ai kā lākou hoʻomohala ʻana.

• ʻOhana Spartan-6:

- Spartan-6 LX FPGA: Hoʻopaʻa ʻia ka loiloi

- Spartan-6 LXT FPGA: Hoʻohui serial kiʻekiʻe

• Hoʻolālā ʻia no ke kumu kūʻai haʻahaʻa

- ʻO nā poloka hoʻohui maikaʻi he nui

- ʻO ke koho maikaʻi ʻia o nā kūlana I/O

- ʻO nā pāpaʻi paʻa

- ʻO nā pūʻolo i hoʻopaʻa ʻia i ka uwea kiʻekiʻe

• Haʻahaʻa static a me ka mana ikaika

- 45 nm kaʻina hana i hoʻopaʻa ʻia no ke kumukūʻai a me ka mana haʻahaʻa

- ʻO ke ʻano hibernate mana iho no ka mana ʻole

- Mālama ke ʻano hoʻokuʻu i ka mokuʻāina a me ka hoʻonohonoho ʻana me ka multi-pin wake-up, hoʻonui mana

- ʻO ka mana haʻahaʻa 1.0V kumu uila (LX FPGA, -1L wale nō)

- Hana kiʻekiʻe 1.2V core voltage (LX a me LXT FPGA, -2, -3, a me -3N mau māka wikiwiki)

• Multi-voltage, multi-standard SelectIO™ interface banks

- A hiki i ka 1,080 Mb/s ka helu hoʻoili ʻikepili no kēlā me kēia ʻokoʻa I/O

- Hiki ke koho ʻia, a hiki i ka 24 mA no ka pine

- 3.3V i ka 1.2VI/O nā kūlana a me nā protocols

- HSTL kumu kūʻai haʻahaʻa a me SSTL mea hoʻomanaʻo

- Hoʻokō hoʻololi wela

- Hiki ke hoʻololi i nā helu pepehi I/O e hoʻomaikaʻi i ka pono o ka hōʻailona

• Nā transceivers serial GTP kiʻekiʻe ma nā FPGA LXT

- A hiki i 3.2 Gb/s

- ʻO nā kikowaena wikiwiki kiʻekiʻe me: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort, a me XAUI

• Poloka Endpoint i hoʻohui ʻia no nā hoʻolālā PCI Express (LXT)

• Kākoʻo ʻenehana PCI® haʻahaʻa haʻahaʻa me ka 33 MHz, 32- a me 64-bit kikoʻī.

• Nā ʻāpana DSP48A1 maikaʻi

- ʻO ka helu helu kiʻekiʻe a me ka hana hōʻailona

- Hoʻonui wikiwiki 18 x 18 a me 48-bit accumulator

- Hiki i ka paipu a me ka cascading

- Pre-adder e kōkua i nā noi kānana

• Nā poloka hoʻoponopono hoʻomanaʻo hoʻohui

- Kākoʻo DDR, DDR2, DDR3, a me LPDDR

- Laki ʻikepili a hiki i ka 800 Mb/s (12.8 Gb/s peak bandwidth)

- ʻO ka hoʻolālā kaʻa kaʻa he nui me FIFO kūʻokoʻa e hōʻemi i nā pilikia manawa hoʻolālā

• Nui nā kumu waiwai noʻonoʻo me ka hoʻonui ʻana i ka mana noʻonoʻo

- Hoʻopaʻa inoa hoʻololi koho a i ʻole kākoʻo RAM hāʻawi ʻia

- Hoʻonui ka LUT 6-input maikaʻi i ka hana a hōʻemi i ka mana

- ʻO LUT me ʻelua kīʻaha paʻa no nā noi pipeline centric

• Block RAM me ka laulā o ka granularity

- Hoʻopaʻa wikiwiki i ka RAM me ka hiki ke kākau i ka byte

- 18 Kb poloka i hiki ke koho ʻia e like me ʻelua mau poloka RAM kūʻokoʻa 9 Kb

• Clock Management Tile (CMT) no ka hoʻonui i ka hana

- Haʻahaʻa haʻahaʻa, hikiwawe ka wati

- Hoʻopau ʻo Digital Clock Managers (DCMs) i ka skew uaki a me ka distortion cycle duty

- Phase-Locked Loops (PLLs) no ka wati haʻahaʻa

- Hoʻohui pinepine me ka hoʻonui like ʻana, ka mahele, a me ka hoʻololi ʻana i ka pae

- He ʻumikūmāono mau pūnaewele uaki honua haʻahaʻa haʻahaʻa

• Hoʻonohonoho maʻalahi, kākoʻo i nā kūlana haʻahaʻa

- 2-pin hoʻonohonoho ʻike ʻakomi

- SPI ākea ʻekolu ʻaoʻao (a hiki i x4) a me ke kākoʻo uila NOR

- Hōʻike i ka Xilinx Platform Flash me JTAG

- Kākoʻo MultiBoot no ka hoʻonui mamao me nā bitstreams he nui, me ka hoʻohana ʻana i ka pale kiaʻi

• Hoʻonui i ka palekana no ka pale hoʻolālā

- Mea ʻike DNA no ka hōʻoia hoʻolālā

- AES bitstream encryption i nā polokalamu ʻoi aku ka nui

• ʻOi aku ka wikiwiki o ka hoʻopili ʻana me ka hoʻonui ʻia, ke kumu kūʻai haʻahaʻa, MicroBlaze™ soft processor

• IP alakaʻi ʻoihana a me nā hoʻolālā kuhikuhi