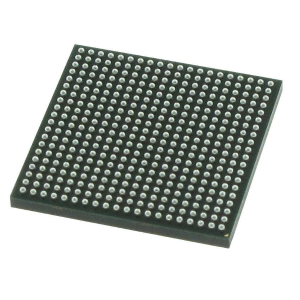

LCMXO1200C-3TN144I FPGA – Māhele Programmable Gate Array 1200 LUTs 113 IO 1.8 /2.5/3.3V -3 Spd I

♠ wehewehe huahana

| Huahana Huahana | Waiwai Hiʻona |

| Mea hana: | Lattice |

| Māhele Huahana: | FPGA - ʻĀpana Programmable Gate Array |

| RoHS: | Nā kikoʻī |

| moʻo: | LCMXO1200C |

| Ka helu o nā Elements Logic: | 1200 LE |

| Ka helu o nā I/Os: | 113 I/O |

| Voltage Hoʻolako - Min: | 1.71 V |

| Voltage Hoʻolako - Max: | 3.465 V |

| Mahana hana liʻiliʻi loa: | - 40 C |

| ʻO ka wela hoʻohana kiʻekiʻe loa: | + 100 C |

| Ka helu ʻikepili: | - |

| Ka helu o nā mea lawe uila: | - |

| Kāila kau ʻana: | SMD/SMT |

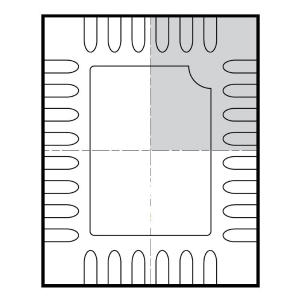

| Pūʻolo/Mahi: | TQFP-144 |

| Packaging: | pā |

| Brand: | Lattice |

| Hoʻolaha ʻia ka RAM: | 6.4 kbit |

| Pākaʻi RAM - EBR: | 9.2 kbit |

| Kiʻekiʻe: | 1.4 mm |

| Ka lōʻihi: | 20 mm |

| ʻO ke alapine hana kiʻekiʻe loa: | 500 MHz |

| ʻAi ʻoluʻolu: | ʻAe |

| Ka helu o nā poloka Lahui Logic - LABs: | 150 LAB |

| Mea Hana i kēia manawa: | 21 mA |

| Voltage lako hana: | 1.8 V/2.5 V/3.3 V |

| ʻAno Huahana: | FPGA - ʻĀpana Programmable Gate Array |

| Ka nui o ka waihona hale hana: | 60 |

| Māhele ʻāpana: | Nā IC Logic Programmable |

| Huina hoʻomanaʻo: | 15.6 kbit |

| laula: | 20 mm |

| Huina Wehe: | 1.319 g |

ʻAʻole hiki ke hoʻonohonoho hou ʻia

• Hikiwawe - hoʻonui i nā mana i nā microseconds

• Hoʻokahi pahu, ʻaʻohe hoʻomanaʻo hoʻonohonoho waho e pono ai

• ʻO ka palekana hoʻolālā maikaʻi loa, ʻaʻohe kahawai e keakea

• Hoʻonohonoho hou i ka manaʻo SRAM ma nā milliseconds

• SRAM a me ka hoʻomanaʻo non-volatile programmable ma o JTAG awa

• Kākoʻo i ka hoʻolālā ʻana o ka hoʻomanaʻo ʻole-volatile

Moe moe

• Hāʻawi iā 100x i ka hoʻemi ʻana i kēia manawa

Hoʻonohonoho hou ʻo TransFR™ (TFR)

• In-field logic update i ka wā e holo ana ka ʻōnaehana

Kiʻekiʻe I/O i Logic Density

• 256 a hiki i 2280 LUT4s

• 73 a hiki i 271 I/Os me nā koho pūʻolo nui

• Kākoʻo ʻia ka neʻe ʻana o ka Density

• Lead free/RoHS compliant packaging

Hoʻokomo ʻia a puʻunaue ʻia

• A hiki i ka 27.6 Kbits sysMEM™ Hoʻokomo ʻia Block RAM

• A hiki i 7.7 Kbits i puunaue i ka RAM

• Hoʻolaʻa manaʻo mana FIFO

Hoʻopaʻa I/O maʻalahi

• Kākoʻo ka polokalamu sysIO™ buffer i ka laulā o nā mea hoʻopili:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

sysCLOCK™ PLLs

• A hiki i ʻelua PLL analog no kēlā me kēia mea

• Hoʻonui ka uaki, puʻunaue, a me ka neʻe ʻana o ka pae

Kākoʻo pae ʻōnaehana

• IEEE Standard 1149.1 Boundary Scan

• Oscillator ma luna o ka moku

• Hoʻohana nā mea hana me 3.3V, 2.5V, 1.8V a i ʻole 1.2V mana lako.

• IEEE 1532 hoʻokō i loko o ka ʻōnaehana polokalamu